在現(xiàn)代電子工程領(lǐng)域,電路設(shè)計已從傳統(tǒng)的紙筆繪圖與物理原型制作,全面轉(zhuǎn)向數(shù)字化、自動化和高度集成的繪圖設(shè)計流程。繪圖現(xiàn)代電子電路不僅是繪制線路圖,更是融合了設(shè)計、仿真、優(yōu)化與制造的一體化工程實(shí)踐,深刻影響著從消費(fèi)電子產(chǎn)品到航天科技的各個領(lǐng)域。

一、現(xiàn)代電子電路繪圖的基石:ECAD軟件

電子計算機(jī)輔助設(shè)計(ECAD)軟件是現(xiàn)代電路繪圖的核心工具。諸如Altium Designer、Cadence OrCAD、KiCad和Eagle等平臺,為工程師提供了從原理圖捕獲到印刷電路板(PCB)布局的全套解決方案。這些軟件允許設(shè)計者以符號化的方式繪制電路原理圖,定義元器件之間的電氣連接,然后自動或手動將其轉(zhuǎn)換為物理PCB布局,精確規(guī)劃走線、過孔、元件放置與信號層。

二、設(shè)計流程的數(shù)字化演進(jìn)

- 原理圖設(shè)計:設(shè)計始于邏輯層面的原理圖繪制。工程師從龐大的元器件庫中調(diào)取符號,定義電源、接地、信號路徑及功能模塊(如放大器、濾波器、微控制器)。現(xiàn)代軟件支持層次化設(shè)計,允許將復(fù)雜電路分解為可管理的子模塊。

- 仿真與驗證:在物理制作之前,電路行為可通過SPICE(仿真程序與集成電路重點(diǎn))等工具進(jìn)行仿真。設(shè)計者能分析直流、交流特性,瞬態(tài)響應(yīng)及信號完整性,及早發(fā)現(xiàn)潛在問題,如噪聲、時序沖突或熱效應(yīng),大幅降低開發(fā)成本與時間。

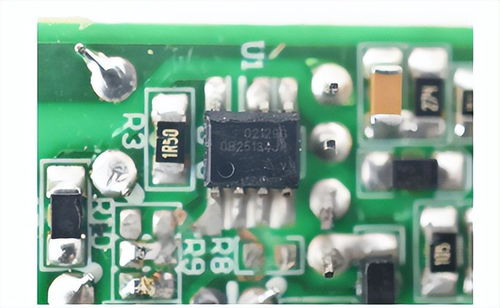

- PCB布局與布線:將原理圖轉(zhuǎn)化為PCB布局是關(guān)鍵一步。軟件提供自動布線功能,但高頻或高密度電路通常需要手動優(yōu)化,以確保阻抗匹配、減少串?dāng)_并滿足電磁兼容性(EMC)標(biāo)準(zhǔn)。3D可視化功能使設(shè)計師能檢查元件間隙、外殼適配及機(jī)械裝配。

- 制造文件輸出:設(shè)計完成后,軟件生成Gerber文件(用于光刻)、鉆孔文件及物料清單(BOM),直接交付PCB制造商。這種無縫銜接實(shí)現(xiàn)了從虛擬設(shè)計到實(shí)體板卡的快速轉(zhuǎn)化。

三、推動革新的關(guān)鍵技術(shù)

- 高密度互連(HDI)與多層板:現(xiàn)代電子產(chǎn)品如智能手機(jī),要求電路板在極小空間內(nèi)承載復(fù)雜功能。HDI技術(shù)利用微孔、埋孔和盲孔實(shí)現(xiàn)多達(dá)數(shù)十層的互連,繪圖軟件需精準(zhǔn)管理這些微觀結(jié)構(gòu)。

- 柔性電路與剛?cè)峤Y(jié)合板:可穿戴設(shè)備和折疊屏手機(jī)催生了柔性電路的需求。繪圖工具現(xiàn)已支持柔性層設(shè)計,模擬彎曲狀態(tài)下的電氣性能與應(yīng)力分布。

- 系統(tǒng)級集成與芯片設(shè)計:對于集成電路(IC)本身,繪圖進(jìn)入納米尺度。硬件描述語言(如VHDL、Verilog)與版圖設(shè)計工具(如Cadence Virtuoso)用于繪制晶體管級電路,實(shí)現(xiàn)系統(tǒng)級芯片(SoC)的定制。

- 人工智能與自動化:AI開始輔助電路優(yōu)化,例如自動布局布線、故障預(yù)測及組件選擇。機(jī)器學(xué)習(xí)算法能基于歷史設(shè)計數(shù)據(jù)推薦高效方案,加速創(chuàng)新周期。

四、未來趨勢與挑戰(zhàn)

隨著物聯(lián)網(wǎng)(IoT)、5G通信和人工智能硬件的普及,電子電路繪圖面臨新挑戰(zhàn):更高頻率(毫米波)、更低功耗、更嚴(yán)格的EMC要求。量子計算與光子集成電路等前沿領(lǐng)域,更將繪圖推向全新維度,需要開發(fā)全新的設(shè)計工具與表示方法。

###

繪圖現(xiàn)代電子電路已演變?yōu)橐婚T融合電氣工程、計算機(jī)科學(xué)和材料學(xué)的綜合學(xué)科。它不僅是技術(shù)實(shí)現(xiàn)的藍(lán)圖,更是創(chuàng)新思想的載體。從概念到產(chǎn)品的旅程中,精確而高效的繪圖設(shè)計確保了電子設(shè)備的功能、可靠性與經(jīng)濟(jì)性,持續(xù)驅(qū)動著數(shù)字時代的科技進(jìn)步。